Thermal performance simulation of phase-change memory cells

Published in 2020

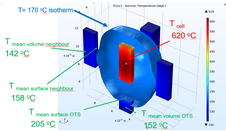

The well-known Moore’s ‘Law’ sets a target for the down-scaling of silicon-based electronic devices. The down-scaling of devices may provide better performances, such as increased speed and lower power consumption that lead to a lower cost per bit. This is true for the processor technologies, the memory technologies such ‘Flash’ and DRAM devices, but also for phase-change memories (PCMs). One of the most serious issues in PCM scaling is the thermal disturbance caused by neighbor cells. The aim of the study was to develop a computational model to simulate temperatures inside phase-change memory cells. In the presentation, we will show some results and discuss the problems we faced.